We were not aware that @conservancy is financed by Google. Thanks for pointing this out!

The choice of including the Software Freedom Conservancy (SFC) in the paper was inspired by the role of Bradley M. Kuhn in the creation of the Affero GPL (https://sfconservancy.org/blog/?author=bkuhn).

Since an involvement of Google conflicts with our standards (as stated in our statute https://wiki.f-si.org/index.php/F-Si_Statute), we have removed the SFC from the white paper. Anyhow, they have not provided any feedback to it.

We prepared a white paper for the #EuropeanCommission containing recommendations about #OpenHardware as encouraged last November:

https://wiki.f-si.org/index.php/White_paper_for_the_EC,_January_2020

Please discuss it or endorse it by replying to this thread.

The paper will be delivered on January 31.

A first draft was shared in December with:

* april.org @aprilorg

* fsfe.org @fsfe

* fsf.org @fsf

* Aral Balkan @aral

* waag.org @waag

* sfconservancy.org @conservancy

* gpl-violations.org

* commonsnetwork.eu

What are the limitations of existing free and open-source (FOS) electronic design automation (#EDA) tools?

What is it missing to design a chip with 1+ Million gates?

Which will be the first foundry to open a process design kit (PDKs)?

These are some of the questions that will be addressed at the third Free Silicon Conference (#FSiC2020) which will be held in Zurich on June 4-6 2020.

More info at:

https://wiki.f-si.org/index.php/FSiC2020

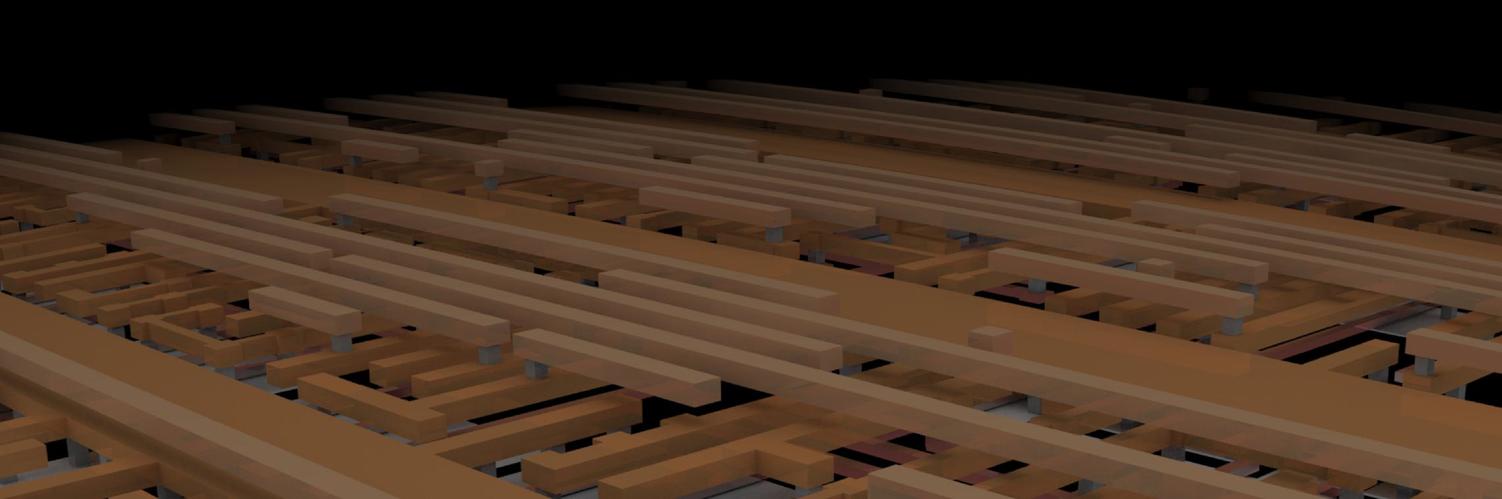

Picture: the Raven chip of Tim Edwards

https://peertube.f-si.org/videos/watch/e8404429-4d32-4741-ac11-1beb0f16348e

#KiCad joins the Linux Foundation to advance electronic design automation

The European Commission is organizing a "Workshop about the future of Open Source Software and Open Source Hardware", Brussels, November 14-15 2019:

Online registration will close on November 6.

Is it possible to simulate transistors using open-source tools only?

How fast are the available solvers?

How hard is it to interface with existing PDKs?

The following talks provide very promising answers:

* ngspice - an open source mixed signal circuit simulator, by Holger Vogt

https://peertube.f-si.org/videos/watch/62e7ad36-e7fc-4884-971a-9fcedf17d9f2

* Gnu Circuit Analysis Package (GnuCap), by Al Davis

https://peertube.f-si.org/videos/watch/5cae10a1-c5c6-45d3-9ade-949c0d3a2062

* Converting 45nm transistor netlists to open standards, by Thomas Benz

https://peertube.f-si.org/videos/watch/40e29b80-8a91-445c-b3cc-1fb886d7d51b

Which foundries are the most friendly to open-source? Is there an open-source #PDK?

Kholdoun Torki of Circuits-Multi-Projects (https://mycmp.fr/) provided a great overview:

"Towards Foundry PDKs on Free CAD Tools"

https://peertube.f-si.org/videos/watch/db22ddc7-85cf-4356-bc46-af90e3f72fd6

All the recordings of the Free Silicon Conference are now online:

https://peertube.f-si.org/video-channels/fsic2019

Day 1 focuses on high-level design. Some of the concepts presented in the first talks can be partially applied to FPGAs as well

Day 2 discusses aspects closer to silicon, such as PDKs, memory generators and layouting

Day 3 presents hands-on tutorials

The full program is available at:

https://wiki.f-si.org/index.php/FSiC2019

The past Free Silicon Conference was opened with a great talk by Todd Weaver from #Purism:

"The Future of Computing and Why You Should Care"

https://peertube.f-si.org/videos/watch/d8dcaf9e-88c7-44cf-9f97-d7d96d1d9b28

We proudly announce to run our own #peertube instance to host the videos of the past Free Silicon Conference 2019:

Is it possible to design a silicon chip using 100% Free and Open Source (FOS) tools?

Can one publish the layout?

Which impact can be expected?

These are few of the questions that thirty-six speakers will address at the second Free Silicon Conference (#FSiC).

Last chance to attend: reservation deadline is next week (February 21):

https://wiki.f-si.org/index.php/FSiC2019

Cannot join in Paris? No worries! We are preparing the equipment to record all the sessions.

Tomorrow (Sunday February 3) the "CAD and Open Hardware" conference will take place at #FOSDEM (Brussels):

https://fosdem.org/2019/schedule/track/cad_and_open_hardware/

Last year's edition (with video-recordings):

https://archive.fosdem.org/2018/schedule/track/cad_and_open_hardware/

Twenty-seven speakers have already confirmed their presence at the Free Silicon Conference (#FSiC):

https://wiki.f-si.org/index.php/FSiC2019#Confirmed_invited_talks

The high-level design session will include speakers from:

1. Gaut (http://www.gaut.fr/)

2. GHDL (http://ghdl.free.fr/)

3. SpinalHDL (https://github.com/SpinalHDL)

Twenty-five speakers have already confirmed their presence at the Free Silicon Conference (#FSiC):

https://wiki.f-si.org/index.php/FSiC2019#Confirmed_invited_talks

The introduction on Day 1 will begin with talks of:

1. Purism (https://puri.sm/)

2. Wiring (http://wiring.org.co/)

3. Echopen (http://www.echopen.org/)

Which impact will the first free and open (layout included) chips have on security, education and cooperative projects?

The 35th Chaos Communication Congress, #35C3, ended few days ago. All talks can be seen at

https://media.ccc.de/c/35c3

and browsed by theme:

https://halfnarp.events.ccc.de/

A small selection about #silicon and place-and-route tools:

LibreSilicon - decentralizing semiconductor manufacturing

https://media.ccc.de/v/35c3-9410-libresilicon

The nextpnr FOSS FPGA place-and-route tool

https://media.ccc.de/v/35c3-9612-the_nextpnr_foss_fpga_place-and-route_tool

OpenCores is specialized on FPGAs:

https://opencores.org/maintainers/oliscience

However, HDL code alone is not sufficient for silicon. It is just one input for the design loops involving place-and-route, parameter-extraction, timing-analysis, etc.

By creating FOS CAD tools we are bridging the gap between HDL and layouts.

Not all CAD tool vendors publish part or all of their licenses, hence the list below is not exhaustive:

https://www.synopsys.com/verification/prototyping/haps/synopsys-license-agreement.html (section 2.2 comma 3)

http://s3.mentor.com/company/enduser-english.pdf (section 4.1)

Those using such tools should refer to the text of their licenses directly.

Where can you download, modify and share a silicon IP block just like you do, say, with gcc?

Nowhere.

The licenses of mainstream proprietary silicon CAD tools explicitly forbid publishing anything created with them. This is partially due to keep algorithms, such as place-and-route, more secret.

It is like writing a book with a proprietary word processor and then not having permission to publish it for not revealing how the grammar checker works.

Free silicon requires free CAD tools.

Totally agree.

In HiFive/SiFive just a small portion of the source/documentation is open, and it is not free (no copyleft license). Nor are the tools to generate the layout.

We want to change that - see the conference program: https://wiki.f-si.org/index.php/FSiC2019

- Website

- https://f-si.org

- Conference

- https://wiki.f-si.org/index.php/FSiC2019

- Videos

- https://peertube.f-si.org